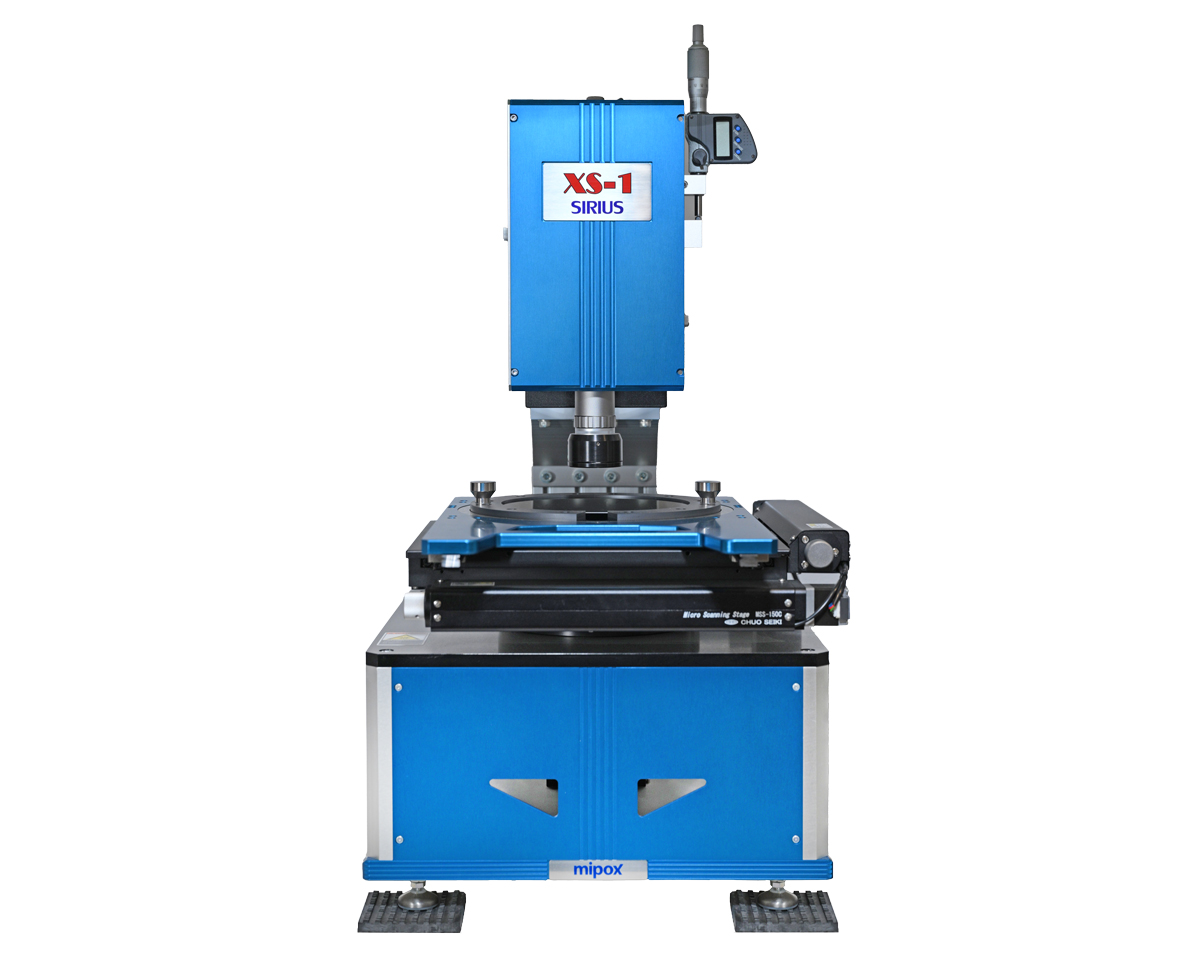

Crystal Dislocation High-Sensitivity Visualization Device XS-1 Sirius

Crystal Dislocation High-Sensitivity Visualization Device XS-1 Sirius

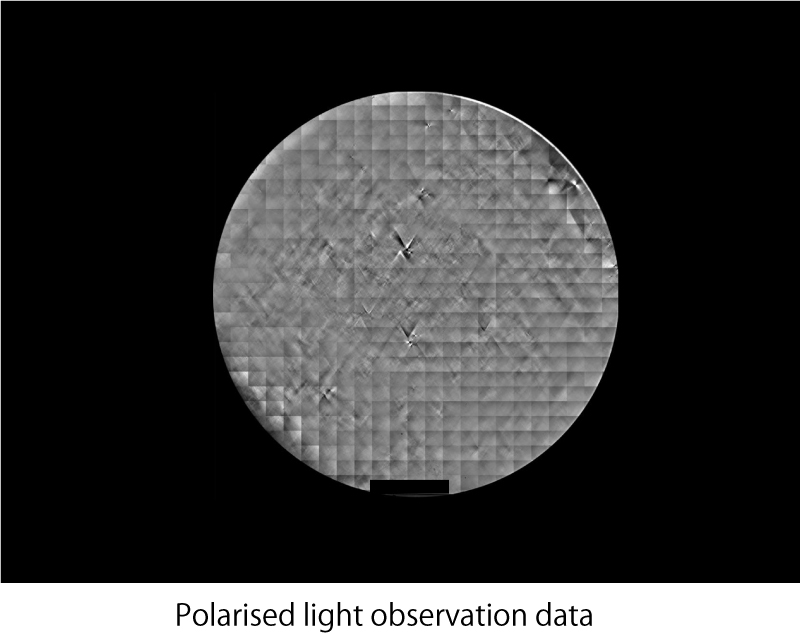

This is a visualization device for dislocations inside semiconductor crystals using polarized light.

■ Revolutionary crystal dislocation detection is possible through proprietary optical theory, as an alternative to etching and X-ray topography

■ No complex adjustments needed - high-speed, high-precision observation is possible simply by setting the workpiece

■ Despite its robust body structure, it is compact and lightweight, enabling space-saving footprint

Product Shape

Applications

Product Features

The XS-1 Sirius is a device that provides real-time, high-sensitivity visualization of crystal-derived defects (such as micropipes, threading edge dislocations, and threading screw dislocations) present within semiconductor wafers used for power devices, exemplified by Silicon Carbide (SiC).

Traditionally, the observation, evaluation, and analysis of dislocations within semiconductor crystal wafers primarily relied on destructive testing methods such as KOH etching, or observation using X-ray topography at large synchrotron radiation facilities, which posed challenges in terms of convenience and cost. To address these challenges, the XS-1 Sirius approaches the solution from an entirely different perspective of optical observation. It achieves non-destructive, low-cost visualization of internal crystal dislocations through a proprietary optical observation system that utilizes crystal-specific birefringence characteristics (retardation) associated with polarized light, combined with phase difference calculation technology.

Submittable Data

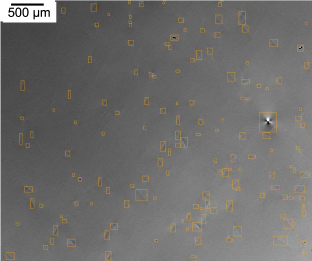

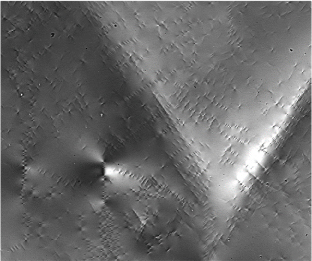

Threading dislocations within the crystal (threading mixed dislocations, threading screw dislocations, threading edge dislocations) and micropipes are visualized as contrast generated by retardation.

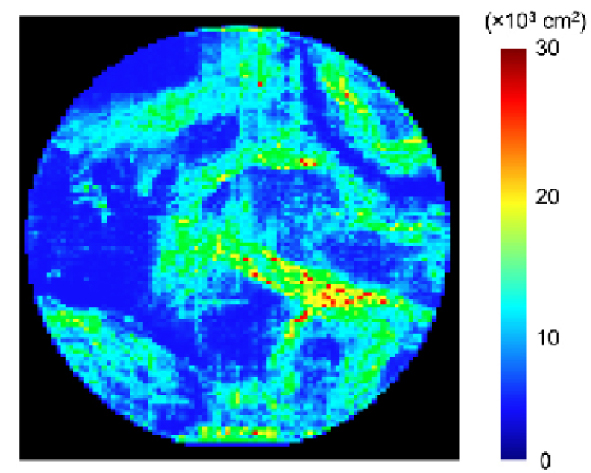

It is possible to count the total number of dislocations in the wafer and display the dislocation density as a color map (heat map).

Currently, we mainly provide the above data through commissioned observation services.

Heat map of the threading dislocation density

Extraction of Through-Transfer using Dislocation Count System

Examples of Threading Dislocations Observation

Compatible Formats

3, 4, 6-inch wafers (8-inch support planned), irregularly shaped chips